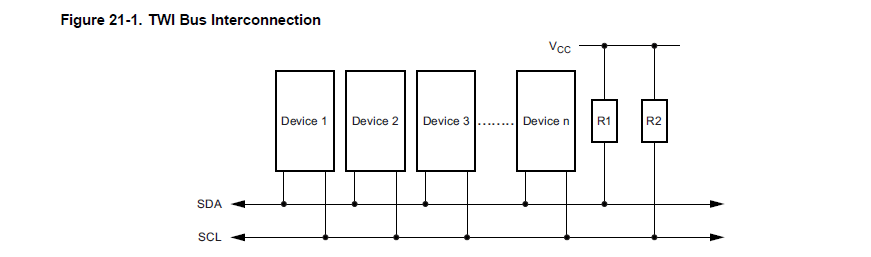

TWI 통신은 2 개의 선만으로 1개의 마스터와 많은 수의 슬레이브와 통신할 수 있는 동기 통신 방식으로 SDA (데이타)

와 SCL(클럭) 선으로 구성되어 있다.

여러개의 마스터를 가지는 기능을 지원하긴하지만 여기서는 다루지 않겠습니다.

주의 할점은 이 두 선은 모두 기본적으로 high 상태이고 모두 수 k옴의풀업저항을 가진다.

이러한 구조는 1개의 슬레이브가 low 신호를 보내면 선 자체가 low 가 되며 다른 회로에서 어떤짓을 하더라도 low

유지 된기 때문에 신호 선점 문제에서 유리한 강점을 가집니다.

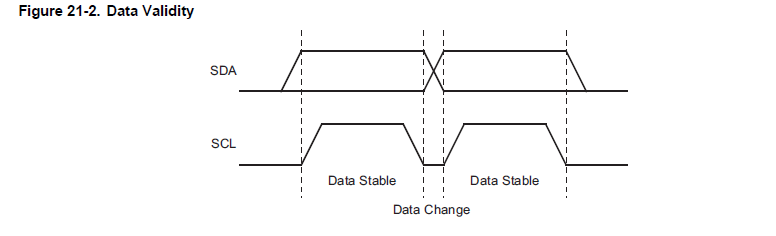

데이타 전송의 경우 클럭이 high 일 경우 SDA 는 변하지 않아야 합니다. SCL 이 low 일 경우에만 SDA 값을 변경 해야 합니다. (뒤에 나오지만 stop start 신호를 인식하기 위해서입니다. )

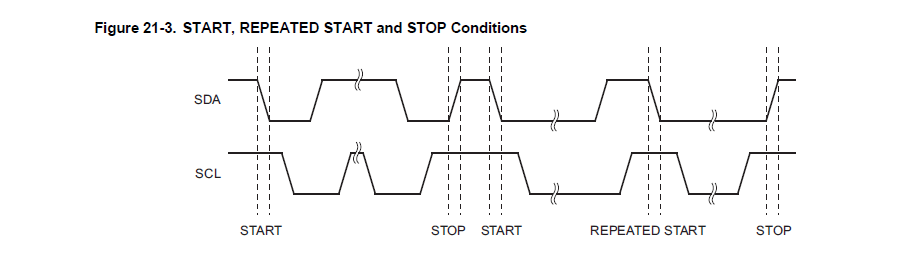

START and STOP Conditions

2선만으로 통신을 한다면 사실 많은 제약이 존재합니다. 특히 1선은 클럭선임으로 실질적으로 우리는 1개의 선으로 통신을 하기 때문에 마스터와 슬레이브간에는 많은 규칙이 존재하고 이를 지켜야지 올바로 통신을 할 수 있습니다.(통신프로토콜)

이에 대한 첫번째로 start stop condition 에대해서 이야기 해보겠습니다.

위의 그림을 보면 아까이야기 한 부분가 다른 부분을 볼수 있습니다. start , stop ,Repeated start , 인 부분에서는 클럭선이 high 를 유지하고 있음에도 sda 의 값이 변하고 있습니다.

대부분의 기기에서는 이러한 edge를 감지할 수있기 때문에 우리는 이를 통해서 데이터 통신이 시작되고 끝나는 지를 알수 있습니다.

scl 이 high 일때 sda 가 high to low 로 변화 한다면 start ( 데이터 통신시작) 을 의미하고

low to high 이면 stop (통신끝) 을 의미합니다. 이러한 약속을 ic2 통신이 가지고 있기 때문에 다른 데이터를 전송할때는 절때 scl 신호가 high 일때 sda 값이 변화하면 안되는 것입니다.

cf) Repeated start 의 경우 데이터 통신중에 또 다른 데이터 통신을 시작 해야하는 경우가 생길 수 있기 때문에 위와 같은 기능을 추가해 놓았습니다.

Repeated start 는 start 신호를 보낸후 stop 신호가 보내지지 않고 또다시 start 신호를 보내면 발생하는 신호입니다.

Combining Address and Data Packets into a Transmission

앞에서 ic2 통신은 여러가지 규칙을 가진다고 했습니다. 여기서는 통신되는 데이터 포멧에 대해 알아보니다.

ic2 통신의 경우 데이타는 왼쪽의 주소 부분과 , 오른쪽의 데이타 부분으로 나뉩니다.

주소(그림 왼쪽)

ic2 는 1대의 마스터가 여러대의 슬레이브와 통신하기 위해서 각가의 슬레이브는 주소를 가지고 있습니다.

때문에 마스터에서 그림의 왼쪽 주소부분에 특정 슬레이브의 주소를 넣으면 그 주소를 가진 슬레이브가 활성화 되고 특정 슬레이브와 통신이 가능해지는 것입니다.

이러한 주소부분은 7bit 의 주소부분과 , r/w (읽기 0 ,쓰기 1) , 그리고 슬레이브가 주소를 수신완료를 알리는 ACK bit 가 존재 합니다.

마스터 쪽에서 주소 7bit 와 r/w 1bit 를 보내면 주소가 일치하는 슬레이브는 sda 신호선을 low 로 당겨서 수신완료 신호(ACK) 를 보내야 합니다.

cf ) 대부분의 주소는 그냥 사용해도 되나 0000 000 은 모든 슬레이브에게 동일한 데이터전송을 위해서 예약되어 있습니다. 또한 1111 xxx 주소 또한 미래에 사용될 목적으로 제한되어 있습니다.

데이타 (그림 오른쪽)

주소부 통신이 완료된후 마스터는 데이터 8bit를 전송하게 됩니다. 슬레이브 측에서는 송신이 완료되면 주소를 수신했을때와 마찬가지로 sda 선을 low 당겨서 ACK 신호를 보냅니다.

만약 9번째 clk(ACK) 때 sda 가 high 라면 마스터기기는 오류가 발생했음을 인지하게 됩니다.

데이타 송신은 SLA +w/l 신호와 stop 신호 사이에 존재하며, 여러번 반복될수 있습니다.(여러 바이트를 연속해서 보낼수 있다. 이는 소프트 웨어적으로 내가 정함)

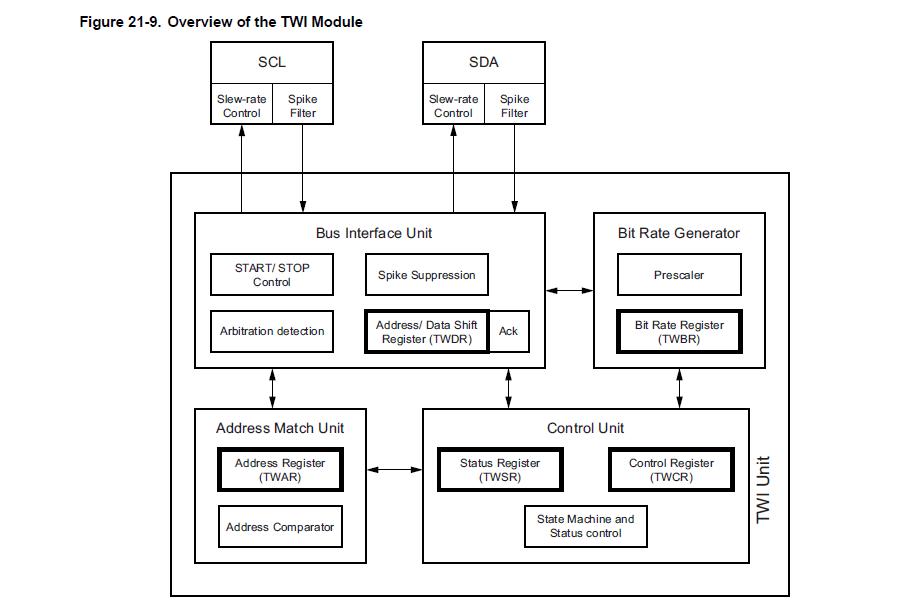

Overview of the TWI Module

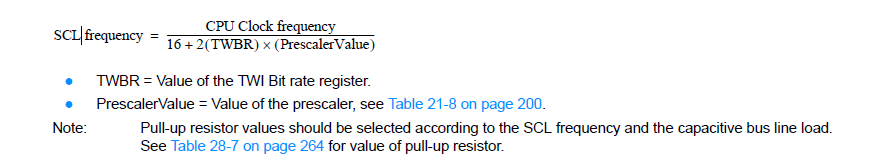

SCL frequency 구하는 공식

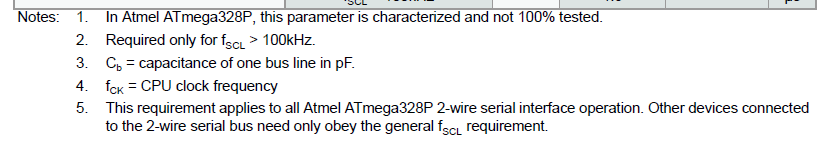

Cb 의 경우 scl , sck 선이 가지는 cap 으로 솔직히 계산하기 힘들다 .

대충 단위가 pF 이라 하면 10pF 이라 해도 (1000n / 10p = 10^5), 100K 옴은 넘는다고 생각하자.

레지스터

IC2 통신동작에는 각가의 레지스터가 어떻게 동작하는 지 꼭알아야 한다. 때문에 레지스터 부분을 먼저 설명하겠다.

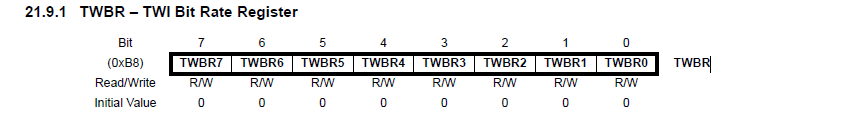

21.9.1 TWBR – TWI Bit Rate Register

• Bits 7..0 – TWI Bit Rate Register

SCL 를 구할때 쓰이는 공식에 나오는 값을 가지고 있다. 위 레지스터를 통해서 SCL 클럭을 조절한다.

TWCR – TWI Control Register

• Bit 7 – TWINT: TWI Interrupt Flag

TWI 가 현재 작업을 완료하면 1로 set 된다. 즉 TWI 가 현재 하는 작업을 완료하고 소프트 웨어적으로 일을 처리할때 1로 set 되서 소프트웨어 적인 일을 기다린다.

여기소 소프트웨어 적인 일이란 TWAR, TWSR ,TWDR 에 접근해서 데이터를 쓰는일이다.

TWINT 가 1로 set 되어 있을때는 SCL 이 LOW 상태를 유지한다 즉 실질적으로 TWI 의 동작이 멈춰있음을 의미한다.

TWINT 플레그를 0 으로 clear 한다면 TWI 가 다시 동작을 한다는 의미이다.

때문에 TWINT 플레그를 0으로 clear 하기 전에 TWAR, TWSR ,TWDR 레지스터에 접근해서 각단계에서 실행해야 되는 일을 한 후 TWINT 플레그를 0으로 clear 해야한다.

신기한 점은 글로벌 인터럽트 벡타가 1로 설정 되어 있을때 TWINT 플레그가 1이되면 TWI interrupt 가 실행 되며지만

다른 인터럽트 플레그와 달리 자동으로 clear 되지 않는다

꼭 TWINT 에 1을 적어줘서 0으로 clear 해줘야 한다.

Bit 6 – TWEA: TWI Enable Acknowledge Bit

1로 set 되어 있을때 밑의 조건을 갖추었을 때 ACK(Low) 신호 생성하도록 하는 bit 이다.

만약 0으로 clear 되어 있다면 ACK 신호가 발생하지 않아서 실질적으로 TWI 통신이 꺼져있다고 봐도 무방하다.

조건

1. 슬레이브 모드에서 자신과 일치하는 어드레스를 수신한 경우

2. TWAR 레지스터에서 TWGCE =1 로 설정되어 있고 전체 호출이 검출된 경우

3. 마스터 수신모드 또는 슬레이브 수신 모드에서 1 바이트 데이터를 수신한 경우

- 조건을 보면 결국 데이터를 수신하고 transmitter 에게 수신했다는것을 알리는 경우이다.

• Bit 5 – TWSTA: TWI START Condition Bit

1로 set 되면 TWI 가 마스터로 동작하면서 start 신호를 보낸다.

이때 TWI 버스가 사용중인지 채크하여 만약 동작중이라면 stop 신호가 검출된후 start 신호를 보낸다.

start 신호가 출력 되었다면 이 비트는 소프트웨어에 의해서 clear 되어야한다.

(start 신호가 출력 되면 TWINT 가 1로 set 된다. 이를 통해서 start 신호가 송신되었는지 판단한다)

• Bit 4 – TWSTO: TWI STOP Condition Bit

마스터 모드에서 1로 set 되면 stop 조건을 출력하며 , TWSTA 와 달리 stop 조건을 수행후 자동으로 clear 된다.

슬레이브 모드에서 1로 set 하면 stop 조건을 출력하는 것이 아니라 TWI 가 에러 상태에서 해제 되면서 정상적인 수신대기 상태가 된다.

• Bit 3 – TWWC: TWI Write Collision Flag

TWINT 가 0일때 TWDR 에 값을 쓰려고 하면 1로 set 된다. 즉 TWI 가 동작중에 데이터가 써지는 경우 에러가 나는것을 표시한다.

TWINT 가 1일때 TWDR 에 값을 쓰면 자동으로 clear 된다.

• Bit 2 – TWEN: TWI Enable Bit

TWI 통신 모듈이 동작하게 해준다. SDL , SCL port 가 TWI 를 위해 사용되게 설정된다.

• Bit 0 – TWIE: TWI Interrupt Enable

TWINT 가 1로 set 됬을때 TWI interrupt 가 발행하도록 해준다.

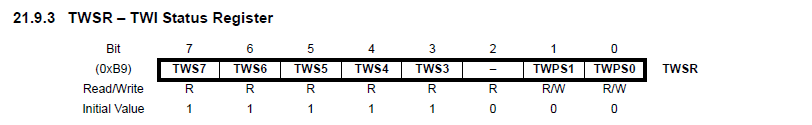

TWSR – TWI Status Register

• Bits 7..3 – TWS: TWI Status

TWI 모듈의 버스 상태를 표시하는 레지스터이다.

TWI 모듈은 총 4가지 모드가 존재하는데

마스터 송신 ,마스터 수신

슬레이브 송신, 슬레이브 수신 모드가 존재한다.

각각의 모드에 따라 7~3bit 는 동작이 달라지기 때문에 데이터 시트를 보고 활용하도록 하자

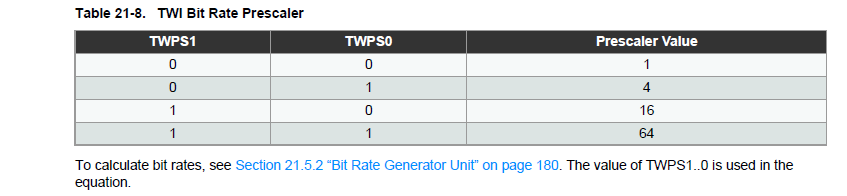

• Bits 1..0 – TWPS: TWI Prescaler Bits

위의 SCL 주파수 공식에 쓰이는 레지스터

분주비를 나타낸다.

TWDR – TWI Data Register

전송 모드에서는 데이터 혹은 슬레이브의 주소를 갖는 레지스터 항상 TWINT 가 1로 set 되어있을떼 write 동작을 한다.

슬레이브 주소를 전송할 경우 앞의 7 bit에는 주소를 마지막 0번 biti는 R/W 를 알려주는 bit 를 넣는다.

수신 모드에서는 송신된 데이터를 갖는다.

TWAR – TWI (Slave) Address Register

슬레이브 모드에서 7bit 의 슬레이브 주소를 저장하는데 사용 ,

Bit 0 – TWGCE: TWI General Call Recognition Enable Bit

만약 1로 set 되어 있다면 전체송출(0000 000주소) 에 대해서 동작하도록 한다.

TWAMR – TWI (Slave) Address Mask Register

• Bits 7..1 – TWAM: TWI Address Mask

해당 bit 에 대한 주소에 마스크를 씨웁니다.

해다 비트가 일치하는지 안하는지 무시하는 기능을 가지게 됩니다.

즉 마스크가 1111 000 으로 되어 있다면 address 의

앞의 4자리 숫자가 어떻 듯 상관하지 않고 뒤의 3자리 숫자만 같으면 해당 슬레이브가 동작 합니다.

'공부,일 > atmega328P' 카테고리의 다른 글

| atmega328P TWI(I2C) 통신 (3) 실습 (0) | 2021.08.07 |

|---|---|

| atmega328P TWI(I2C) 통신 (2) (0) | 2021.08.05 |

| atmega 328p USART (3) 실습 (0) | 2021.08.02 |

| atmega 328p USART (2) 레지스터 (0) | 2021.08.02 |

| atmega 328p USART (1) 개념 및 다이어그램 (0) | 2021.08.01 |

댓글