19.10.1 UDRn – USART I/O Data Register n (0xC6)

USART 는 특이하게 송신 , 수신 하는 데이터 레지스터를 공유한다. 정확히 말해서는 각각의

transmit data buffer shift register , receive data buffer shift registers 가지고 있지만 직접 접근 할 수 는 없다.

UDRn 레지스터를 통해서 각가의 레지스터에 접근 가능한데

UDREn flag 가 set 되어 있을때 UDRn 레지스터에 데이터를 입력하고 ,transmit data buffer shift register 가 비어 있다면 ,데이터를 shift register 에 적는다 그리고 바로 TxDnb pin 으로 전송한다.

19.10.2 UCSRnA – USART Control and Status Register n A (0xC0)

• Bit 7 – RXCn: USART Receive Complete

데이터를 다 받고 나면 1로 set , cpu 가 이를 읽어서 수신 버퍼가 비면 , 0 으로 clear

또는 receive complete interrupt 를 일으키면 0 으로 clear

• Bit 6 – TXCn: USART Transmit Complete

the transmit shift register 가 모든 bit 를 shift 하고 , UDRn 레지스터에 아무 데이터가 없다면 1로 set

이는 transmit complete interrupt 가 발생하면 자동으로 clear 된다.

또는 이 bit 를 1로 적으면 clear 된다.

• Bit 5 – UDREn: USART Data Register Empty

transmit buffer (UDRn) 가 데이터를 받을 준비가 되면 set 된다.

송신 버퍼에 새로운 데이터를 쓰거나 , register empty interrupt 를 실행하면 0 으로 clear 된다.

시스템 reset 시 이 비트는 1이 디폴트 값이다.

• Bit 4 – FEn: Frame Error

frame error 의 발생여부를 알려주는 bit 이다.

수신데이터의 첫번째 stop bit가 0 이면 1로 set 된다.

이 플랙은 UDRn 을 읽거나 다음 데이터의 stop bit 가 1이면 clear 된다.

UCSRnA 레지스터를 라이트하면 항상 clear된다.

• Bit 3 – DORn: Data OverRun

Data OverRun 에러를 감지하는 bit 이다. overRun 에러는 수신 버퍼에 아직 읽지 않은 데이터가 있을때

수신 시프트 레지스터에 새로운 데이터가 들어올때 1로 set 된다.

이 플랙은 UDRn 을 읽으면 0으로 clear 된다.

UCSRnA 레지스터를 라이트하면 항상 clear된다.

• Bit 2 – UPEn: USART Parity Error

parity error 가 발생했을때 1로 set

이 플랙은 UDRn 을 읽으면 0으로 clear 된다.

UCSRnA 레지스터를 라이트하면 항상 clear된다.

• Bit 1 – U2Xn: Double the USART Transmission Speed

비동기 모드에서 2배속 모드를 적용하기 위한 bit

1 로 set 되면 클럭 분주비를 16 에서 8로 낮춰서 전송 속도를 2배로 높인다.

• Bit 0 – MPCMn: Multi-processor Communication Mode

멀티 프로세싱 모드로 전환하기 위해서 사용

멀티 프로세싱모드는 1대1통신이아닌 1대 M 통신으로 각각의 주소를 가지고 있고 , 내가 원하는 주소의 장비와 통신하는 방식이다.

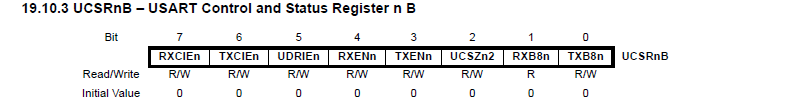

19.10.3 UCSRnB – USART Control and Status Register n B (0xC1)

• Bit 7 – RXCIEn: RX Complete Interrupt Enable n

the global interrupt flag 가 1이고, RXCn flag 이 1일때

RX Complete Interrupt 가 발생하도록 해준다.

• Bit 6 – TXCIEn: TX Complete Interrupt Enable n

the global interrupt flag 가 1이고, TXCn flag 이 1일때

TX Complete Interrupt 가 발생하도록 해준다.

• Bit 5 – UDRIEn: USART Data Register Empty Interrupt Enable n

the global interrupt flag 가 1이고, UDREn 이 1일때

Data Register Empty Interrupt가 발생하도록 해준다.

• Bit 4 – RXENn: Receiver Enable n

USART 가 수신부로 동작하게 해준다. TxDn pin 이 병렬 포트가 아니라 송신용 핀으로 동작하게 해준다.

또한 FEn, DORn, and UPEn flags 가 동작하도록 하용한다.

• Bit 3 – TXENn: Transmitter Enable n

USART 가 송신부로 동작하게 해준다. RxDn pin 이 병렬 포트가 아니라 수신용 핀으로 동작하게 해준다.

또한 FEn, DORn, and UPEn flags 가 동작하도록 하용한다.

만약 송신 중간에 이 bit 가 0으로 clear 되더라도 송신을 완료한후 효력을 발휘 한다.

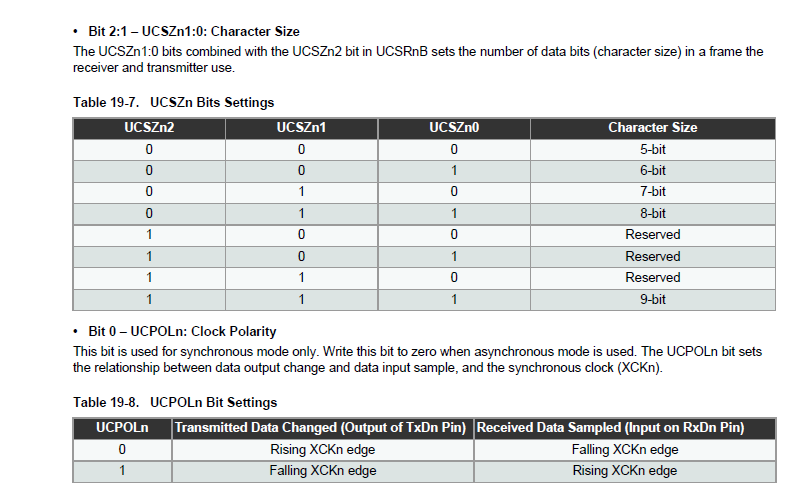

• Bit 2 – UCSZn2: Character Size n

전송할 데이터의 크기를 설정

• Bit 1 – RXB8n: Receive Data Bit 8 n

전송 문자가 9 개로 설정된경우 8번째 bit 를 저장하는 bit 이다.

항상 UDRn 레지스터보다 먼저 읽어져야 한다.

• Bit 0 – TXB8n: Transmit Data Bit 8 n

전송 문자가 9로 설정될 경우 8번째 bit를 저장하는 bit 이다.

항상 UDRn 레지스터보다 먼저 써져야 한다.

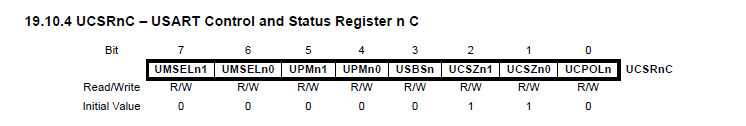

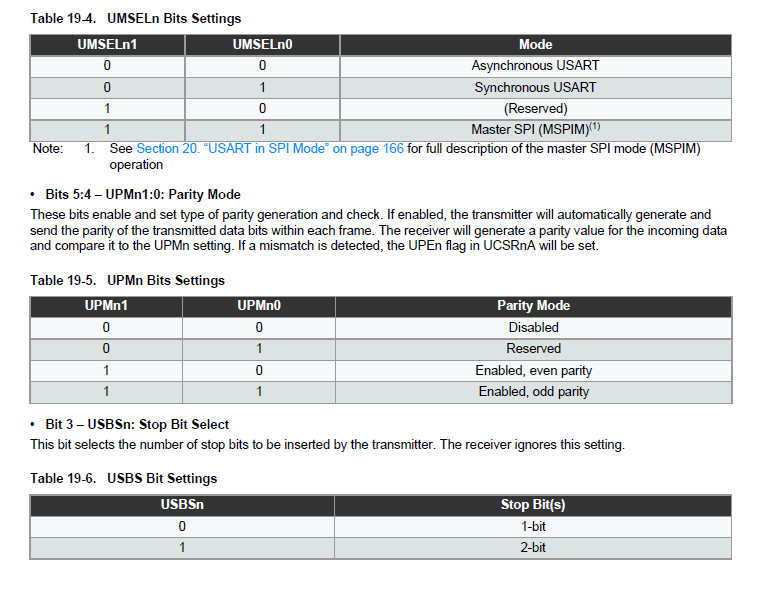

19.10.4 UCSRnC – USART Control and Status Register n C (0xC2)

7~3 bit

2~0 bit

• Bit 0 – UCPOLn: Clock Polarity

동기 전송 모드에서만 효력이 있으며 ,송,수신이 XCKn 클럭의 상승 , 하강 엣지에서 sampling 할지 정한다.

19.10.5 UBRRnL(0xC4) and UBRRnH(0xC5) – USART Baud Rate Registers

송수신 보더레이트를 설정하는 레지스터 이다. (좀 범위가 넓은 분주기이다.)

16 bit 레지스터는 항상 H 를 먼저 라이트하고 L 을 라이트 한다.

사실 위의 레지스터로 정확한 보러 레이트를 얻기는 힘들다 ( 위의 레지스터 값은 정수 값으로 정확한 보러 레이트를 얻고 싶다면 실수 범위를 다뤄야함 )

이렇게 실수를 다룰 수 없기 때문에 생기는 오류가 존재 하는데 밑의 표는이 오류를 표로 정리해 놓았다.

아두이노는 16MHz 임으로 위의 표를 적용하면 된다.

'공부,일 > atmega328P' 카테고리의 다른 글

| atmega328P TWI(I2C) 통신 (1) 개념 및 레지스터 (0) | 2021.08.05 |

|---|---|

| atmega 328p USART (3) 실습 (0) | 2021.08.02 |

| atmega 328p USART (1) 개념 및 다이어그램 (0) | 2021.08.01 |

| 질문 (0) | 2021.07.30 |

| atmega 328p SPI(2) 실습 (0) | 2021.07.29 |

댓글