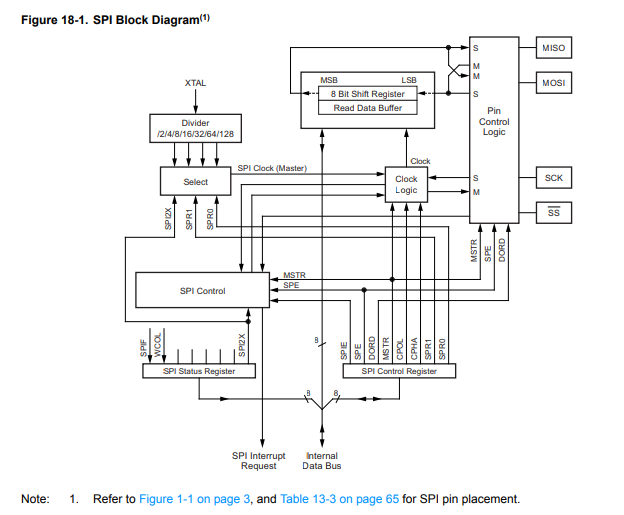

SPI 통신은 직렬 통신방법중의 1개로써 동기 통신이다.

때문에 입력선 , 출력선 , 클럭선이 필요하고

SPI 는 특수하게 제어 선(SS) 가 필요하다.

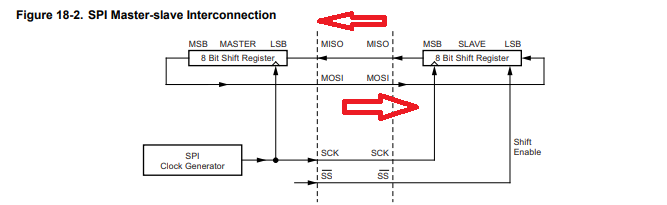

SPI 통신은 위와 같이 Master mode 와 Slave mode 가 존재하고 1대의 Master 가 여러대의 Slave 와 통신하는 구조이다. 어떤 Slave 와 통신 할지는 SS 선에 들어오는 신호를 감지하고 결정한다.

SPI 가 정상 작동 하기 위해서는 SCK 가 (CPU CLK)/2 이하가 되어야 된다고 한다.

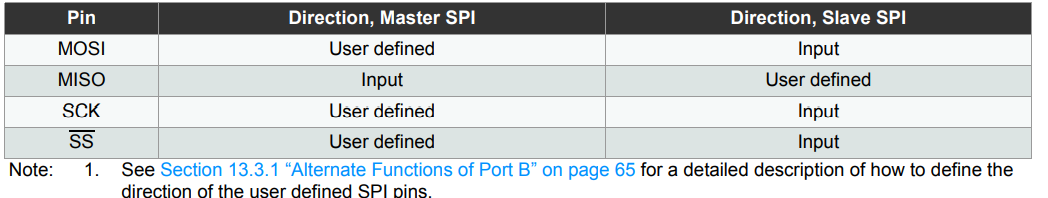

각 모드별 핀 입 출력 방향

마스터 슬레이브 통신

SPI 통신은 양방향 통신으로 송신과 수신이 동시에 일어난다. 1BIT 씩 송신하고 동신에 1BIT 씩 수신하고 있다.

때문에 실질적으로 데이터 수신 송신 과정은 16 BIT 순환 SHIT RAGISTER 라고 생각하면된다.

참고 블로그

https://webnautes.tistory.com/994

Atmega128 기초 - SPI(Serial Peripheral Interface)

Atmega128의 SPI에 대해 간단히 설명하고 포스트 끝에 마스터와 슬레이브 예제를 제공합니다. 2016. 6. 29 최초작성 2021. 7. 18 최종작성 SPI (Serial Peripheral Interface)를 사용하면 AVR과 주변 장치 간 또..

webnautes.tistory.com

마스터가 슬레이브에게 테이터 송신

1.송신 할려고 하는 슬레이브 SS 선을 L 로 한다.

2.SCK 핀에서 클럭 신호 출력

3. MOSI 단자로 출력 .

4. 전송이 끝나면 SS 신호를 H 로 돌려 슬레이브를 정지 시킨다.

Master Mode

마스터의 경우 SS 신호선은 단순한 병렬 I/O port 로 사용할수 있다. DDRx 레지스터로 출력 용으로 설정 해라

그러나 만약 Master Mode 에서 입력으로 설정 된다면 무조건 풀업 저항과 같은 외부회로로 H 를 유지하도록 해야한다.

만약 SS Pin 이 입력 mode 에서 L 상태가 되면

Master Mode 가 해제되고 Slave Mode 로 변경된다.

또한 SPSR 레지스터의 SPIF 가 1로 set 되면서 SPI Serial complete 인터럽트가 발생한다.

즉 Master 에서 slave 모드로 변경하고 싶지 않다면 SS 핀은 출력으로 설정해 놓아야 한다.

송신할 슬레이브를 정했다면

그후에는 SPDR 레지스터에 전송할 데이터를 입력하면 자동으로 8bit Shift 하여 데이터를 전송한다.

데이터 전송이 끝나면 SPIF = 1 로 set 되면서 전송완료 인터럽트가 발생한다.

Slave Mode

슬레이브 모드에서는 SS 핀이 자동으로 입력핀으로 동작하고 SS 핀이 L 일때 슬레이브로서 동작하게 된다.

SS 핀이 H 일때 데이터 레지스터에 값을 라이트 하더라도 SS핀이 L 상태가 될때까지 대기한다.

SS핀이 L 상태에서 데이터 레지스트터의 1 byte 가 전송되고 나면 SPIF = 1 로 set 되면서 전송완료 인터럽트가 발생한다.

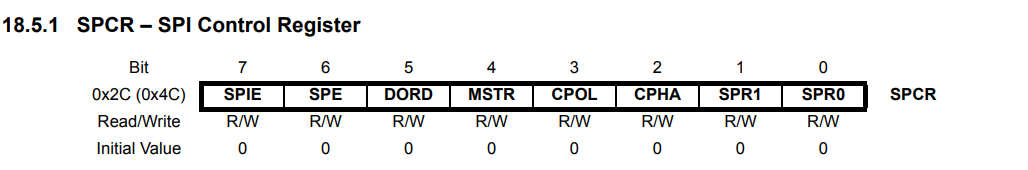

레지스터

SPCR – SPI Control Register

• Bit 7 – SPIE: SPI Interrupt Enable

SPI interrupt 가 발생하도록 해준다.

• Bit 6 – SPE: SPI Enable

1로 set 해서 SPI 가 동작하도록 해준다.

• Bit 5 – DORD: Data Order

1로 set 되면 LBS bit 먼저 전송되고

0로 clear 되면 MBS bit 먼저 전송 된다.

• Bit 4 – MSTR: Master/Slave Select

1로 set 되면 master 모드로 동작하고

0로 clear 되면 slave 모드로 동작한다.

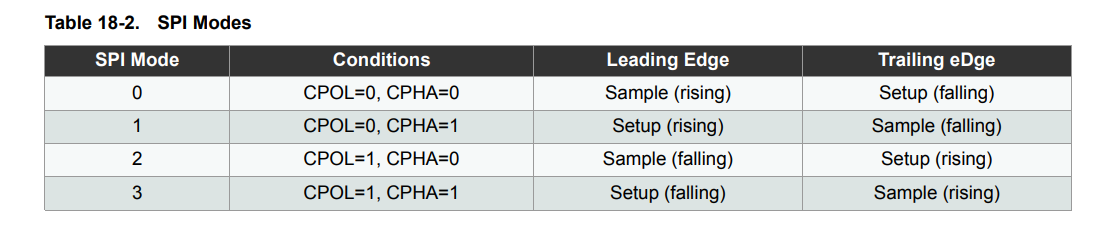

• Bit 3 – CPOL: Clock Polarity

• Bit 2 – CPHA: Clock Phaser

SPI Mode 를 설정한다.

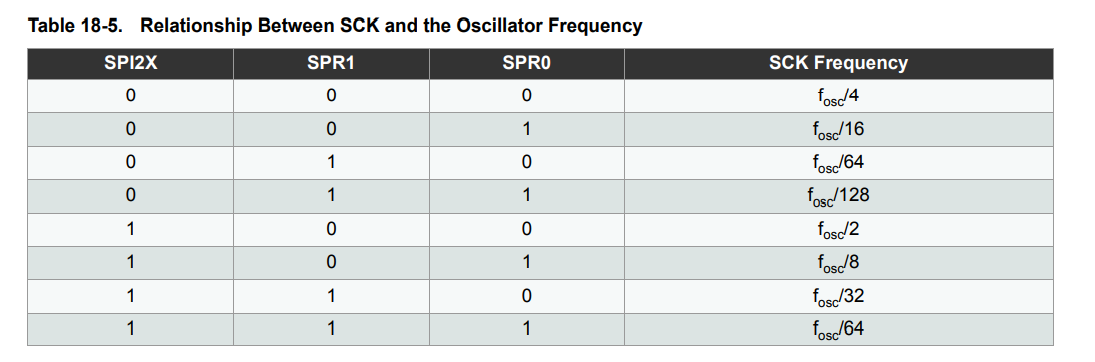

• Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

SCK 클럭 수를 조절해준다. (cpu 클럭에다가 나눔)

slave 모드일때는 아무 영향을 주지 않는다

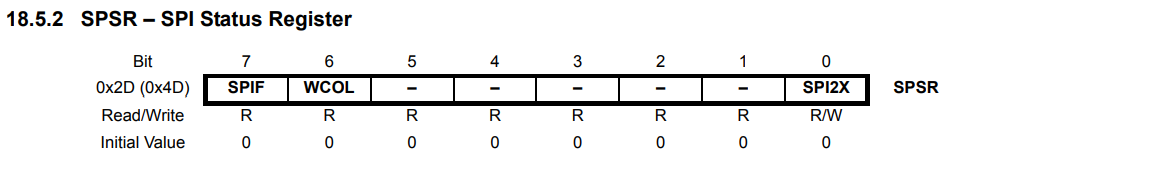

SPSR – SPI Status Register

• Bit 7 – SPIF: SPI Interrupt Flag

데이터 shift 가 완료 되면 SPIF 가 1 로 set 되고 SPIE 가 set 되어 있다면 SPI interrupt 가 발생한다.

FLAG 가 클리어 되는 조건은 2가지가 존재한다.

첫번째는 인터럽트 벡타가 수행되면 1로 초기화 된다.

두번째는 SPSR 레지스터가 읽어진 후 SPDR(데이터레지스터) 에 접속이 일어나면 자동으로 클리어 된다.

• Bit 6 – WCOL: Write COLlision Flag

데이터 전송중 SPDR 에 데이터가 입력 되면 1로 set 된다.

사용자가 SPSR 레지스터를 읽고나서 다시 SPDR 레지스터를 엑세스 하면 SPIF 와 WCOL 비트는 클리어 된다.

•Bit 0 – SPI2X: Double SPI Speed Bit

SCK 클럭 주파수가 2배가 된다.

18.5.3 SPDR – SPI Data Register

특이한점은 송신 버퍼로 사용되는 경우는 단일 버퍼로 동작하며 , 수신 버포로 사용되는 경우에는 이중 버퍼로 동작한다.

'공부,일 > atmega328P' 카테고리의 다른 글

| 질문 (0) | 2021.07.30 |

|---|---|

| atmega 328p SPI(2) 실습 (0) | 2021.07.29 |

| 링커스크립트 (0) | 2021.07.29 |

| 좋은 블로그 atmega 관련 (0) | 2021.07.29 |

| atmel studio 설치 및 hex 파일 업로드 (아두이노 우노) (0) | 2021.07.29 |

댓글