기본 개념

atmega328 의 경우 8 채널 10 bit 의 분해능을 가진 축차 비교형 ADC 이다.

축차 비교형 컴버터의 동작원리 :

축차 비교형 아날로그-디지털 변환회로 - 위키백과, 우리 모두의 백과사전

축차 비교형 ADC 기능도 아날로그-디지털 변환회로 방식중에 축차 비교형 아날로그-디지털 변환회로(Successive approximation ADC)는 이진 탐색 방식으로 양자화하는 변환 방식이다. 내부에 DAC와 비교기

ko.wikipedia.org

ADC 의 경우 단일 변환 모드(single conversion mode)와 프리 러닝 모드(free running mode)가 존재한다.

단일 변환 모드는 아날로그 신호가 한 번만 변환되고 , 프리러닝 모드는 계속해서 A to D 변환이 진행된다.

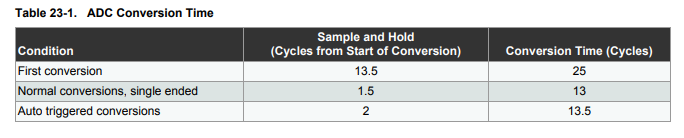

ADC 동작에 걸리는 clk 를 나타냈으며 clk는 ADC 분주기로부터 얻은 클럭이다.

sample and hold 에 소모되는 클럭수는 conversion time 안에 포함된다.

input voltage 범위

conversion 할 아날로그 input voltage 번위는 0 ~ AREF까지 이다. 설정에 따라서 AVcc 또는 1.1v 가 될 수도 있다.

즉 축차비교형 ADC의 기준 전압(Vref ) 값 까지 번위를 가질 수이다.

주파수

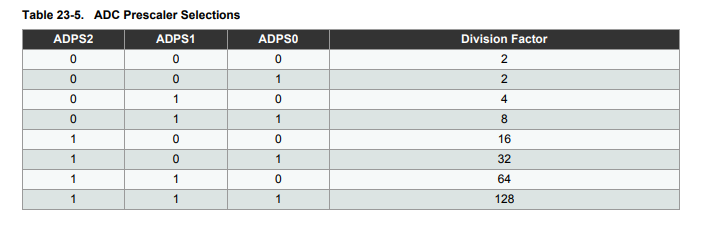

데이터 시트에서 free running mode에서 가장 좋은 분해능을 가지기 위해서는 50kHz ~ 200kHz의 주파수를 필요로 한다고 나와있다. 이러한 주파수를 얻기 위해서 ADC 에는 분주기가 존재하는데 다음 그림과 같이 동작하고

ADPSn 은 다음의 레지스터 파트를 읽어보면 어떻게 사용할지 알 수 있다.

CK는 cpu의 클럭이다. 우리는 16 Mhz의 외부 크리스털을 사용함으로 CK = 16 M이다.

16M / 128 하면 125kHz 임으로 우리가 원하는 주파수 범위이다. 따라서 분주비는 128로 한다.

분해능

10bit 분해능을 가지고 있으므로 위와 같이 표현될 수 있다.

레지스터

ADMUX

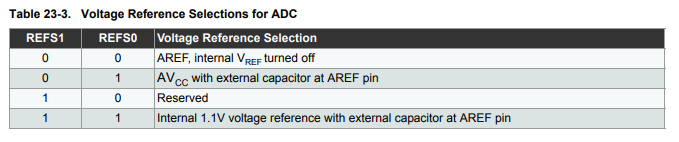

Bit 7:6 – REFS1:0: Reference Selection Bits

- 축차 비교형 ADC에 사용되는 AREF를 선택하는 bit이다.

표를 보면 알다시피 AVcc와 , internal 1.1v를 사용하기 위해서는 AREF pin 에다가 cap을 꼿 아야 하기 때문에

나는 AREF(0,0)를 사용하겠다

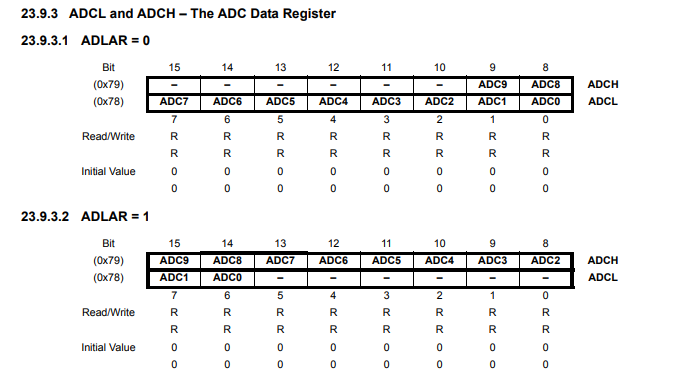

Bit 5 – ADLAR: ADC Left Adjust Result

ADC data register를 좌측 정렬 할것인지 우측 정렬 할 것인지 정함 , 1일때 좌측정렬

Bits 3:0 – MUX3:0: Analog Channel Selection Bits

어떤 채널을 사용할 것인지 설정

cf (atmega128의 경우 차동 입력까지 지원하지 마 32의 경우는 단극성 입력만 지원)

ADCSRA – ADC Control and Status Register A

• Bit 7 – ADEN: ADC Enable

1로 set 하면 adc 가 사용 가능

• Bit 6 – ADSC: ADC Start Conversion

ADSC는 conversion 이 수행 중에는 1로 set 되어 있고 수행 후 자동으로 clear 된다.

free running mode 다시 자동으로 1로 set 되어서 변환이 자동으로 수행된다.

• Bit 5 – ADATE: ADC Auto Trigger Enable

1로 set 하면 auto trigger를 사용할 수 있다. auto trigger는 ADCSRB 레지스터에서 다룬다.

• Bit 4 – ADIF: ADC Interrupt Flag

conversion 이 완료되고 data register를 갱신한 후 1로 set 된다.

SREG의 I bit 가 1이라면 ADC conversion complete interrupt 가 발생하고 인터럽트가 처리되면 다시 0으로 clear 된다.

• Bit 3 – ADIE: ADC Interrupt Enable

1로 set 되면 ADC conversion complete interrupt 가 발생 가능하다.

• Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

ADC의 분주비를 선택한다.

ADCL and ADCH – The ADC Data Register

conversion 된 데이터를 저장하는 레지스터 ( 정렬 방식에 따른 차이 )

ADCSRB – ADC Control and Status Register B

Bit 6 – ACME : analog comparator multiplexer enable bit

아날로그 비교기에서 8개의 아날로그 input 채널을 사용하기 위한 bit

ADC를 사용할 때는 항상 0으로 clear 되어야 한다. 1로 set 된다면 아날로그 비교기가 작동하고 ADC는 꺼진다.

• Bit 2:0 – ADTS2:0: ADC Auto Trigger Source

triger mode를 결정하는 bit

ADCSRA 레지스터의 ADATE bit 가 1일 때 영향을 줄 수 있다.

free running mode를 제외하고는 선택된 인터럽트의 플레그 비트가 set 1로 될 때 conversion 이 실행된다.

free running mode는 인터럽트에 상관없이 계속 실행되는 모드이다.

23.9.5 DIDR0 – Digital Input Disable Register 0

- ADC5:0번 핀 또한 모드 i/O pint 임으로 digital input buffer를 가지고 있다.

아날로그 input pin으로 사용될 때는 digital input buffer를 사용할 필요가 없기 때문에 disable 하게 해줘야 한다.

ADC7, ADC6 pin 은 digital input buffer 가 존재하지 않아서 관련 bit 가 존재 하지 않는다.

• Bit 5:0 – ADC5 D.. ADC0 D: ADC5.. 0 Digital Input Disable

1로 set 하면 각 pin에 연결된 digital input buffer를 사용 불가능하게 만들어 준다.

'공부,일 > atmega328P' 카테고리의 다른 글

| atmel studio 설치 및 hex 파일 업로드 (아두이노 우노) (0) | 2021.07.29 |

|---|---|

| atmega328P ADC (2) 프로젝트 실습 (0) | 2021.07.28 |

| atmega 328p PWM & timer counter (5) 실습 Fast PWM (0) | 2021.07.27 |

| atmega 328p PWM & timer counter (4) 실습 (Normal mode) (0) | 2021.07.27 |

| atmega 328p PWM & timer counter (3) mode (0) | 2021.07.27 |

댓글